Projects / iThemba Labs

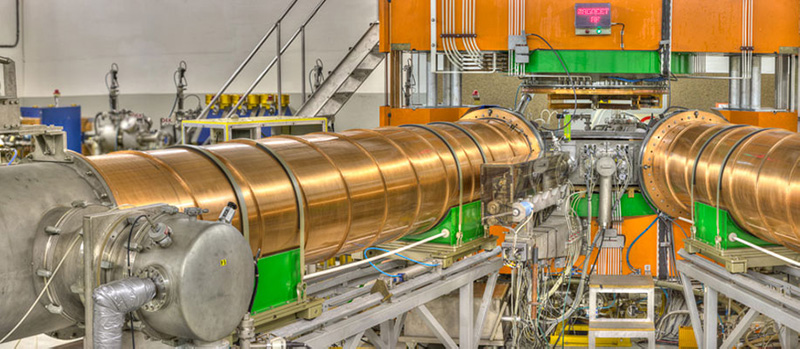

I spent a few months over my 3rd year vacation period interning at the iThemba Laboratory for Accelerator-Based Sciences in Cape Town. The facility had a dorm, where I stayed with other interns. During the day we worked on different software projects. By night, we roamed the (fortunately disabled) proton beam lines.

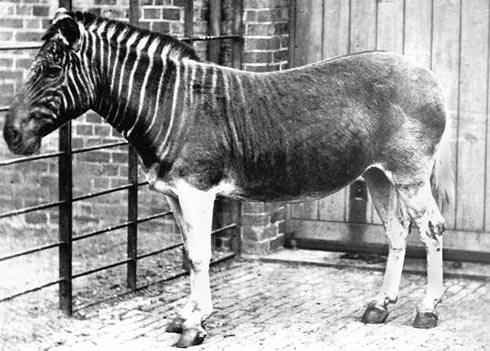

There was no one there on weekends, but two things kept it from being dull. First, the facility bordered the KhayelitshaWikipedia township, so we could enjoy cheap beer from the local shebeen and get to know the neighbours. Second, the bizarre quagga breeding projectquaggaproject.org used the grounds of the accelerator to house their attempts to “recreate” the now-extinct quaggaWikipedia from horse and zebra stocks, so there were odd animal hybrids wondering around to keep us company.

My job was to play around with so-called field-programmable gate arraysWikipedia. My mentor Sean Murray had bought some Altera Cyclone FPGAs in the hope they could be used to replace iThemba’s particle detection trigger circuitry, which was at the time wired up completely by hand. This made the detection circuits hard to document, reproduce, and debug, so the plan was to replace them with fully virtual circuits in the form of VHDLWikipedia descriptions that could be downloaded to the Cyclone hardware.

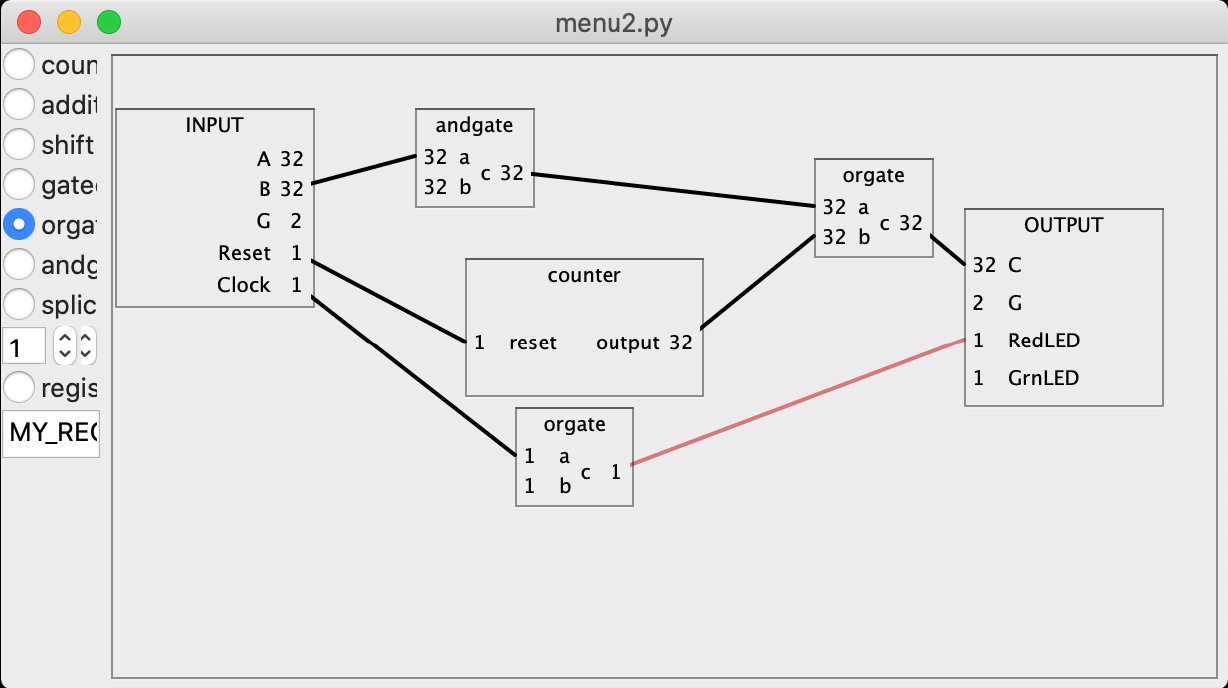

I set to work writing a GUI in Python that could allow arbitrary wiring-together of raw chunks of functionality, like AND gates and delay lines, such that an experimental physicist could produce circuits without having to learn the expensive, proprietery Altera software, or write any VHDL code themselves.

Here is what my software looked like (unfortunatelly updates to wxPython since then have made the GUI slightly bug out):

When you constructed these virtual circuits in the GUI, it would automatically infer the “bus widths” of the connections between individual logic blocks, a primitive form of the kind of type inference you see in modern compilers. The available blocks (shown cut-off in the left hand side) were automatically parsed and imported from generic VHDL code that looked like this:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_arith.all;

USE ieee.std_logic_unsigned.all;

USE ieee.std_logic_misc.all;

entity orgate is

generic (width : positive);

port(a : in std_logic_vector (width-1 downto 0);

b : in std_logic_vector (width-1 downto 0);

c : out std_logic_vector (width-1 downto 0));

end orgate;

architecture rtl of orgate is

begin

summing: process (a, b)

begin

c <= a or b;

end process;

end rtl;

By the end of my stint at iThemba, I got the whole system to actually work end-to-end. You could design a circuit, click a button, and have it deployed to a rack of Cyclones in no time. For the intern demo day, I was able to wheel out a huge rack of LEDs, build a circuit on my laptop, and have the an LED start blinking! Which was probably anti-climactic for my managers after spending so much money on the Cyclones, but a succesfull proof of principle nonetheless!

I do not know what happened to my prototype after my internship was over – I imagine it is gathering dust somewhere. But I do know the pseudo-quagga are still roaming the iThemba LABS grounds. I’m sure they will outlast many technology cycles to come!